# Design and evaluation of a phase-shift full-bridge converter for electrical vehicle

Shisong Wang, Yuanxiong Duan, Jinhao Ruan, Zhanghai Shi Department of Electrical Engineering, Southwest Jiaotong University, Chengdu, China E-mail: shizhanghai@163.com

Abstract –A high frequency converter with maximum 150A/2.5kW output is designed and evaluated in this paper. This converter consists of three parallel PSFB modules. The main components for each module are designed. Small signal model for single module is established and a digital peak current mode control is designed and implemented. Finally, a 2.5kW prototype with up to 150A output current is built. The experimental results demonstrate well performance of the prototype and confirm of the validity the design.

Keywords – phase-shift full-bridge; small signal model; peak current mode control

# I. INTRODUCTION

There are many low-voltage electronic devices on electric vehicles, such as air conditioner, wiper, multimedia equipment and lighting system. These electronic devices work with low voltage, but the total current of these loads is high. Therefore, a low-voltage and high-current power supply is required, which converts the high voltage of vehicle power battery to low voltage and provides high current.

Phase-shift full-bridge (PSFB) DC-DC converter have the advantages such as high-power density, low switching loss and large conversion ratio, thus it is wildly applicated in high-power and high-frequency isolated power conversion system.

Series studies on PSFB converter have been carried out [1]-[7]. PSFB ZVS DC-DC converter can realize zero voltage switching (ZVS), thus switching loss can be significantly reduced, but the ZVS range of switches (especially in lag bridge) is limited and may loss ZVS at light load. Many approaches of keeping ZVS of PSFB converter at light load have been reported, for example, an auxiliary circuit attached to the main circuit is designed to achieve ZVS at light load in [3], and [4]-[6] report some control strategies to extent ZVS range. The loss of diode rectifier will be significant under large output current, to increase the efficiency, synchronous rectifier is applied in [7-8] to reduce power loss of rectification circuit, and the power loss of synchronous rectifier is analyzed in [8].

Peak current mode control (PCMC) is widely used in control of DC power supply attributed to the advantages such as inherent over current protection, automatic current sharing in parallel operation. In [9] and [10], PCMC is applicated to control the isolated DC-DC converter, and the digital slop compensation of PCMC is studied in [11].

In this paper, a high-current power converter which consists of three PSFB modules is designed and evaluated. To reduce loss, rectifier diodes are replaced by MOSFETs to achieve synchronous rectifier. A resonant inductor is applicated to extend the soft switching range. Each module has a double-current-loop controller to regulate the output current. PCMC is used as the inner-loop controller which can prevent the transformer saturation.

The rest of this paper is organized as follows. In section II, the circuit topology and parameter design are introduced; to design the controller, the small signal model is established in section III; and the experimental results of a 2.5kW prototype are presented in section IV. Finally, in section V, some conclusions are presented.

II.

## DESIGN OF MAIN CIRCUIT

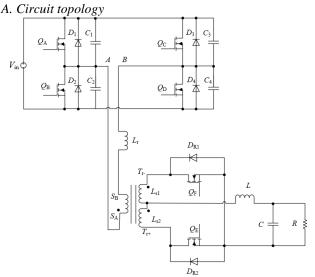

Fig. 1: The topology of synchronous rectified PSFB circuit

Fig.1 is the topology of single PSFB converter with synchronous rectifier. The primary side is a full-bridge inverter consists of MOSFET Q1~Q4, and the secondary side is a synchronous rectifier circuit, using MOSFET with lower on-resistance to replace diodes, thus the loss of rectifier can be effectively reduced, and the efficiency of converter can be increased. In Fig. 1,  $C_1 \sim C_4$  are the parasitic capacitance of MOSFET. Usually, their capacitance is not large enough to implement soft switching. It is necessary to add extra capacitor to them. Lr is the resonant inductor, its value equals to the sum of circuit parasitic inductance and transformer equivalent leakage inductance. The PSFB converter can achieve ZVS through the resonance of Lr and  $C_1 \sim C_4$ . The turns ratio of transformer is n: 1: 1 which is determined by requirement of input and output voltage range. The circuit of output filter consists of inductor L and capacitor C. And R is the load.

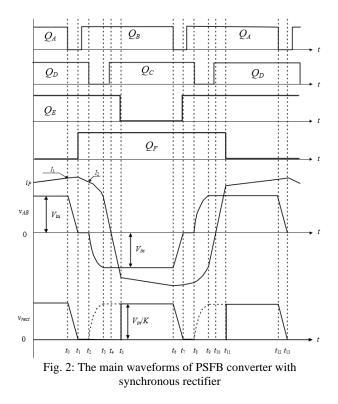

Fig. 2 shows the operation waveforms of PSFB converter with synchronous rectifier. The output voltage of PSFB converter can be adjusted by the phase difference between two bridge legs. And the detailed operation principle can be found in [8].

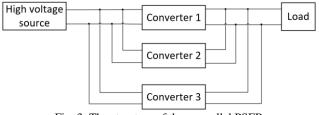

Parallel operation of PSFB modules can increase the output power or current. In the design of this paper, three parallel modules work together as Fig. 3.

Fig. 3: The structure of three parallel PSFB

## B. Design of circuit

The required specifications of the designed PSFB converter include input voltage DC 315-420V, controllable output current ranged from 0A to 150A, the 5A maximum current ripple, and the maximum output voltage 20V. As the converter is composed by three parallel PSFB modules, each module will take a load of 50A.

In PSFB converter, the switches of bridge can achieve ZVS by the resonance between leakage inductor of transformer and parasitic capacitor of switches[1]. An extra resonant inductor can help to keep the ZVS property at light load.

As Fig. 2 shows, the duty cycle of secondary voltage  $V_{rect}$  is smaller than primary voltage  $V_{AB}$ . The duty cycle loss of secondary voltage has been derived in [1]. It is expressed as (1).

$$D_{eff} = D - \frac{2kL_r f_s}{V_{in}} (2I_L - \frac{V_o}{2f_s L} (1 - D))$$

(1)

where k = 1/n is the turns ratio between the secondary side and primary side of transformer,  $f_s$  is switching frequency,  $V_{in}$  and  $V_o$  are input voltage and output voltage,  $L_r$  is the value of resonant inductor and L is the value of output inductor, D is the duty cycle of primary side voltage  $V_{AB}$ .

From (1), a larger resonant inductance  $L_r$  means larger duty cycle loss  $D_{loss}$ , thus the resonant inductor should be set to an appropriate value. In this design, the resonant inductor is set to  $L_r = 16 \ \mu H$ . After some calculations, the parameters of the PSFB in Fig. 1 are designed as Table 1.

Tabla 1. Main airearit a ana araitan

| Table 1: Main circuit parameters |                 |         |

|----------------------------------|-----------------|---------|

| Items                            | Symbol          | Value   |

| Input voltage                    | V <sub>in</sub> | DC 315V |

| Transformer ratio                | n: 1: 1         | 10:1:1  |

| Maximum output voltage           | $V_o$           | DC 20V  |

| Output current                   | Io              | 50 A    |

| Output filter inductor           | L               | 300 µH  |

| Resonant inductance              | $L_r$           | 16 µH   |

| Switching frequency              | $f_s$           | 100 kHz |

| Output filter capacitor          | C               | 5000µF  |

# III. SMALL SIGNAL MODELING AND CONTROLLER DESIGN

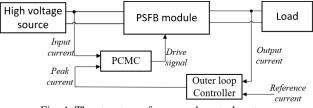

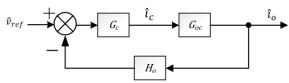

As Fig. 4 shows, a double-current-loop control system is designed to regulate the output current of converter, where inner loop is peak current mode controller. To design the controller of outer loop, small signal model of designed PSFB converter is established in this section.

Fig. 4: The structure of proposed control system

#### A. Modeling of designed PSFB converter

PSFB converter is derived from Buck converter. It is a kind of isolated Buck converter, thus the small signal model of PSFB converter can refer to the model of Buck converter. But the loss of duty cycle and turns ratio of transformer should be considered. According to [1], the effective duty cycle perturbation can be derived as (2).

$$\hat{d}_{eff} = \hat{d} + \hat{d}_v + \hat{d}_i \tag{2}$$

where  $\hat{d}_i$  and  $\hat{d}_v$  are the perturbations of effective duty cycle resulting from the change of output filter current  $i_L$  and the change of input voltage  $V_g$ , respectively. And  $\hat{d}$  is the perturbation of duty cycle.

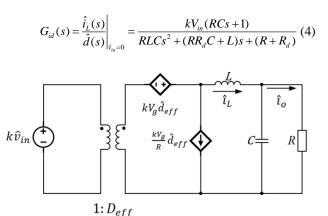

The established small signal model of designed PSFB DC-DC converter is shown in Fig. 5. From Fig. 5, the transfer function from duty cycle  $\hat{d}$  to output current  $\hat{i}_o$  can be derived as (3).

$$G_{od}(s) = \frac{\hat{i}_{o}(s)}{\hat{d}(s)}\Big|_{\hat{v}_{u}=0} = \frac{kV_{in}}{RLCs^{2} + (RR_{d}C + L)s + (R + R_{d})}$$

(3)

where  $R_d = 4k^2 f_s L_r$ .

The transfer function from duty cycle  $\hat{d}$  to output filter inductor current  $\hat{\iota}_L$  is (4).

Fig. 5: Small signal model of designed PSFB DC-DC converter

#### B. Modeling of controller

In this design, input current  $i_g$  is the input of inner-loop, and the feedback factor of current sensor is  $R_s$ . The waveform of PCMC in this PSFB converter is shown in Fig. 6, where  $m_c$ is the slope compensation of peak current  $i_c$  which helps to prevent sub-harmonic of PCMC,  $m_1$  and  $m_2$  are slopes of converted output inductor current  $i_L$ , and the period of  $i_g$ and  $i_L$  is  $T = T_s/2$ .

Fig. 6: Waveform of PCMC in PSFB converter

According to the operating principle of PSFB converter,  $i_g$  is equal to the converted output inductor current  $i_L$  during  $d_{loss}T$  as Fig. 6 shows, thus the average value of  $kR_si_L$  in a period can be expressed as:

$$kR_{s}\langle i_{L}\rangle_{T} = \langle i_{c}\rangle_{T} - m_{c}dT - \frac{1}{2}m_{1}d_{eff}^{2}T - \frac{1}{2}m_{2}\left(1 - d_{eff}\right)^{2}T$$

(5)

where

$$\begin{cases} m_1 = \frac{kR_s \left[kv_g - Ri_o\right]}{L} \\ m_2 = \frac{kR_sRi_o}{L} \end{cases} \end{cases}$$

Removing the higher-order perturbations, the  $\hat{d}$  can be expressed as:

$$\hat{d} = F_d(\hat{i}_c - F_L \hat{i}_L - F_v \hat{v}_{in} - F_o \hat{i}_o)$$

(6)

where  $F_d = \frac{1}{M_c T}$ ,  $F_L = k R_s$ ,  $F_v = \frac{k^2 R_s D_{eff}^2 T}{2L}$ ,  $F_o = \frac{k R_s R (1 - 2D_{eff}) T}{2L}$ .

## C. Modeling of closed-loop system

From equation (3) (4) and (6), the transfer function from control current  $\hat{i}_c$  to output current can be expressed as:

$$G_{oc}(s) = \frac{\hat{i}_{o}(s)}{\hat{i}_{c}(s)}\Big|_{v_{im=0}} = \frac{F_{d}M_{od}(s)}{1 + F_{d}F_{o}M_{od}(s) + F_{d}F_{L}M_{id}(s)}$$

(7)

Thus, the block diagram of small-signal closed-loop system can be established as Fig. 7, where  $H_o$  is the feedback proportional coefficient of output current  $\hat{\iota}_o$ , and  $G_c$  is compensation function of outer-current-loop.

Fig. 7: The block diagram of small-signal closed-loop system

From Fig. 7, the open-loop transfer function can be deduced:

$$T_c = G_{oc} \cdot H_o \tag{8}$$

# D. Controller design

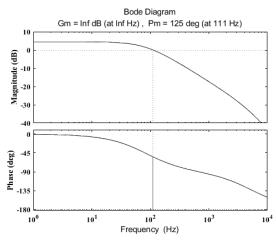

The circuit parameters of this converter are set as Table. I, the resistance of load set to  $R = 0.4 \ \Omega$ , and  $R_s = 51$ ,  $H_o = 9.4$ , the compensation slope of PCMC is set to  $m_c = 3.1 \times 10^6$ , from equation (8), the open-loop transfer function  $T_c$  can be calculated as:

$$T_c(s) = \frac{3.03 \times 10^7}{s^2 + 3.52 \times 10^4 s + 1.8 \times 10^5}$$

(9)

The bode diagram of  $T_c$  is shown in Fig. 8. A simple PI controller  $G_c(s)$  is designed based on the  $T_c$  as equation (10).

$$G_c(s) = 0.1 + 200 \times \frac{1}{s}$$

(10)

Fig. 8: The frequency response diagram of open-loop transfer function  $T_c$

### IV. EXPERIMENTAL RESULTS

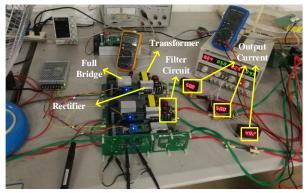

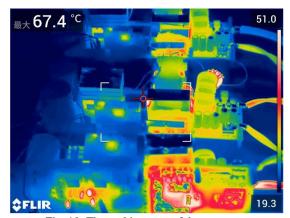

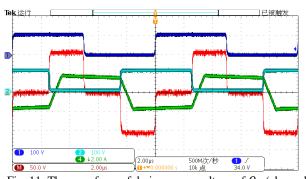

Finally, a prototype of 2.5kW DC-DC converter consists of three parallel PSFB modules is given in Fig. 9, and the thermal imagery is given in Fig. 10. It can be noticed that each module takes 50A output current, and the overall temperature of converter is lower than 70 °C which is within the accepted range. Fig. 11 is the waveform of drain-source voltage of  $Q_B$  (channel 1), drain-source voltage of  $Q_D$  (channel 2), primary side voltage  $V_{AB}$  (channel 3) and primary side current  $i_p$  (channel 4) while input voltage is 100V. It can be noticed that the waveform is stable and ZVS has been achieved.

Fig. 9: Prototype of the three parallel PSFB converter

Fig. 10: Thermal imagery of the converter

Fig. 11: The waveform of drain-source voltage of  $Q_B$  (channel 1), drain-source voltage of  $Q_D$  (channel 2), primary side voltage  $V_{AB}$  (channel 3) and primary side current  $i_p$  (channel 4)

# V. CONCLUSIONS

To provide the high current consumed by lots of electronic loads on electrical vehicle, this paper designs a converter composed of three parallel PSFB DC-DC converters. The design procedures of parameters of the main circuit and controller are presented. The main circuit can realize ZVS. Additional resonant inductor can help to keep ZVS when the load is not large enough. The loss of duty cycle is considered when modelling. The peak current mode control can avoid magnetic saturation of transformer. The experimental results show that the even current sharing is achieved between the three modules. The overall temperature of the converter is within a reasonable range, which indicates the rationality of the design.

#### REFERENCES

- [1] J. A. Sabate, V. Vlatkovic, R. B. Ridley, F. C. Lee and B. H. Cho, "Design considerations for high-voltage high-power full-bridge zero-voltage-switched PWM converter," Fifth Annual Proceedings on Applied Power Electronics Conference and Exposition, Los Angeles, CA, USA, 1990, pp. 275-284, doi: 10.1109/APEC.1990.66420.

- [2] H. Aksoy and M. T. Aydemir, "Comparison of zero voltage switching phase-shifted PWM full bridge DC-DC converter topologies," 2015 Intl Aegean Conference on Electrical Machines & Power Electronics (ACEMP), 2015 Intl Conference on Optimization of Electrical & Electronic Equipment (OPTIM) & 2015 Intl Symposium on Advanced Electromechanical Motion Systems (ELECTROMOTION), Side, 2015, pp. 818-824, doi: 10.1109/OPTIM.2015.7427028.

- [3] A. F. Bakan, N. Altintaş and İ. Aksoy, "An Improved PSFB PWM DC–DC Converter for High-Power and Frequency Applications," in IEEE Transactions on Power Electronics, vol. 28, no. 1, pp. 64-74, Jan. 2013, doi: 10.1109/TPEL.2012.2196287.

- [4] Y. Tang, Y. Wu, Z. Chen, C. Zhang and W. Hu, "Hybrid mode control for wide range soft-switched full-bridge converter with auxiliary parallel inductor networks," in IET Power Electronics, vol. 12, no. 7, pp. 1670-1678, 19 6 2019, doi: 10.1049/iet-pel.2018.6104.

- [5] A. Mallik and A. Khaligh, "Variable-Switching-Frequency State-Feedback Control of a Phase-Shifted Full-Bridge DC/DC Converter," in IEEE Transactions on Power Electronics, vol. 32, no. 8, pp. 6523-6531, Aug. 2017, doi: 10.1109/TPEL.2016.2616033.

- [6] S. Lee, J. Lee, U. A. Khan and J. Park, "Novel Switching Control Method for Synchronous Rectifier of Phase-Shifted Full-Bridge Converter in Light-Load Conditions," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 2019, pp. 1408-1413, doi: 10.1109/ECCE.2019.8912223.

- [7] C. Zhao, X. Wu, P. Meng and Z. Qian, "Optimum Design Consideration and Implementation of a Novel Synchronous Rectified Soft-Switched Phase-Shift Full-Bridge Converter for Low-Output-Voltage High-Output-Current Applications," in IEEE Transactions on Power Electronics, vol. 24, no. 2, pp. 388-397, Feb. 2009, doi: 10.1109/TPEL.2008.2005269.

- [8] L. Hua, J. Guo, X. Jing, N. Mi, R. Chung and S. Luo, "Design considerations for secondary side synchronous rectifier MOSFETs in Phase Shifted Full Bridge Converter," 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 2013, pp. 526-531, doi: 10.1109/APEC.2013.6520260.

- [9] Y. Sun and B. Jiao, "Design of a soft-switched phase-shift full bridge converter," 2016 3rd International Conference on Systems and Informatics (ICSAI), Shanghai, 2016, pp. 230-234, doi: 10.1109/ICSAI.2016.7810959.

- [10] N. Vazquez and M. Liserre, "Peak Current Control and Feed-Forward Compensation for the DAB Converter," 2019 IEEE International Conference on Industrial Technology (ICIT), Melbourne, Australia, 2019, pp. 685-690, doi: 10.1109/ICIT.2019.8755238.

- [11] M. Hallworth and S. A. Shirsavar, "Microcontroller-Based Peak Current Mode Control Using Digital Slope Compensation," in IEEE Transactions on Power Electronics, vol. 27, no. 7, pp. 3340-3351, July 2012, doi: 10.1109/TPEL.2011.2182210.